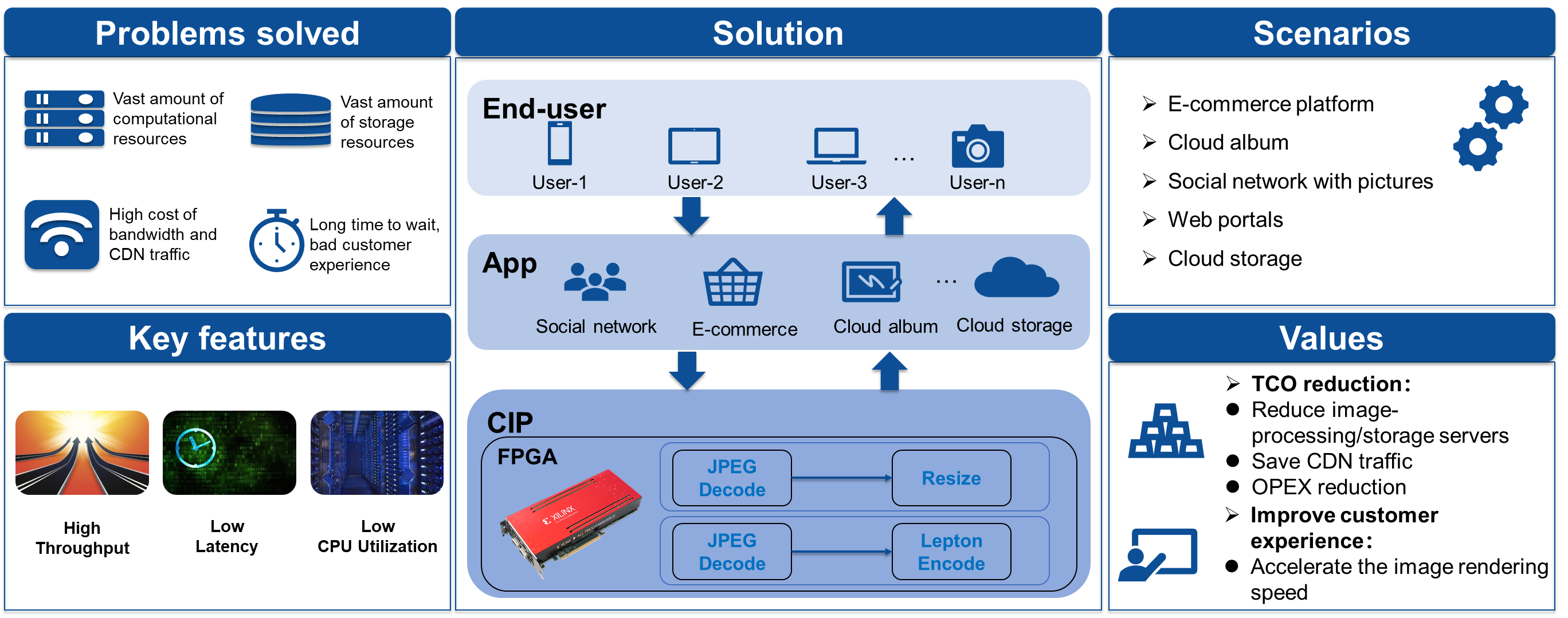

CTAccel Image Processing (CIP) accelerator for Alveo™️ U200

Overview

- Throughput promotion: 4 times more than CPU

- Latency reduction: 4 times less than CPU

- TCO reduction: improve the computing density of DC, reduce racks

- Software compatible: ImageMagick、OpenCV、GraphicsMagick、Lepton

Solution Introduction

Introduction

The popularity of smartphone and social network makes taking and sharing of pictures extremely simple and convenient. As of 2017, there are 2.4 billion active smartphone users worldwide. Images that were taken by smartphone users alone amount to petabytes of data generated every day. Cloud storage has make it easier than ever for mobile phone users to share their pictures in social media and access their picture from multiple devices. As a result, most mobile phone users opt to store their pictures in the cloud. These pictures inevitably end up as image data stored in Internet Data Centers (IDC). As a result, image processing computation such as image transcoding, thumbnail generation, image recognition and the like on these massive image data have become part of IDC computation workload.

The instruction based Von Neumann architecture of CPU and GPU have inherent limitations in running image coding and decoding algorithms, instructions are inherently serial, so there are limitations on utilizing massive data parallelism to improve computational performance.

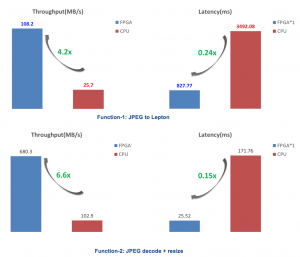

CTAccel Image Processing (CIP) accelerator is an FPGA-based image processing acceleration solution that greatly improves the performance of image processing and image analytics by transferring computational workload from CPU to FPGA. CIP's powerful processing capabilities benefit data centers by increasing image processing throughput by 4-6x, reduce computational latency by 4x, and reduce TCO by 3x. CIP redefines data center image processing with state-of-the-art technologies which utilize massively data parallel algorithm to increase computational performance.

Accelerated Functions

JPEG to Lepton / JPEG decode + resize

Use Case

- Thumbnail Generation 2. Resize 3. Watermark 4. Brightness/Contrast 5. Sharpen 6. Maincolor 7. Image storage

Features and Benefits

High Performance

CIP uses FPGA as a heterogeneous coprocessor on servers to offload the typical image encoding, processing and decoding workflows from CPU. An x86 server with dual E5-2630 CPU equipped with a single CIP accelerator can increase image processing speed by 4-6x while reducing computational latency by 4x.

Low Power

The CIP accelerator has a low power consumption.A single accelerator can increase server performance by 4-6x, thus drastically increase compute density, which translates to less rack space and lower administration cost.

Software compatible

CIP is fully compatible with the most popular open source image processing software: OpenCV , ImageMagick , GraphicsMagick and Lepton. The perfect integration of the mainstream image processing software allows users to migrate seamlessly from software-based implementation to CIP.

Ease of Maintenance

CIP employs advanced FPGA Partial Reconfiguration (PR) technology. The computation cores can be upgraded and reconfigured remotely to maximize the performance for custom usage scenario. PR technology allows fast and easy context switch of accelerator functionality without rebooting the server.

Test Environment

- CPU:2x Intel(R) Xeon(R) CPU E5-2630 v2 @ 2.60GHz

- OS: CentOS Linux release 7.3.1611

- FPGA: AlveoTM U200

- Platform: SDAccel 2017.4